может буфера какие всё же стоят

ZX-Evo Rev. C4 (Double-config) / VDAC2 / ZiFi / NeoGS / ZXM-Soundcard Extreme

нет. новые платы сразу идут с нормальной жесткой дешифрацией, если же есть какие-то конфликты с внутренними портами, то вырабатывают iorqge. на тех платах, которые использует ТС нельзя так сделать, так как используется мягкая дешифрация по большей части и конфликты могут быть уже между самими платами в слотах (наверное только в DivGMX может быть полная дешифрация), а не между платой в слоте и внутренними портами компа.

- - - Добавлено - - -

больше на логику похоже.

Profi must live!

Моё железо...

1. Profi 5.06/1Mb(DRAM)+Profi5.06(UP)/HDD/3`5FDD/CF512Mb/SD-CARD

3. Profi 6.2 Rev. B/1Mb/3`5FDD/HDD3.2Gb

4. Profi 5.05(down)/1Mb+Profi 5.03(UP)/Pentagon_Fix

Все укомплектованы:

Profi_ZX-BUS/ZXMC2/NemoIDE/SounDrive[свернуть]

Ссылка на Telegram-канал поддержки пользователей Profi.

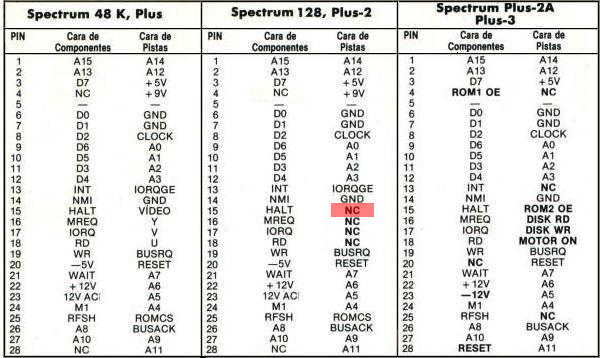

Похоже, что начиная с +2A сигнал IORQGE выкинули.

В сервис мануале на +2B +3B его нет.

Скрытый текст

https://drive.google.com/drive/folde...xZ83juCuaBe32I

Scorpion ZS 256 Turbo+/GMX 2MB/SMUC v1.3 OP/CF-IDE 2GB/TS ARM/Covox #DD/FDD 5'25/FDD 3'5/AT Kbrd & Mouse Ctrl v2.5/Universal PS/2 Kbrd Ctrl/ZX WiFi

Leningrad 1/Sega Joy Adapter

DivGMX

ZX Spectrum +2A

ZX Evolution rev. C

TCK Computer 486DX2-66/512K Tridend 9000i/8MB SIMM72/CF-IDE 512MB/ESS 1869/CNet CN200/FDD 5'25/FDD 3'5

[свернуть]

Они его не поняли.

Из ZaRulem #19:

Глава 2: Адресное пространство портов ZX Spectrum.

Одним из самых распространённых заблуждений о ZX Spectrum, уступающим только мифу о том, что его изобрёл Синклер, является миф, о том, что его единственный физический порт якобы занимает все 32768 чётных адресов в адресном пространстве портов устройств ввода-вывода (УВВ). Давайте разберёмся с истоками этого заблуждения. Действительно, в компьютере ZX Spectrum, дешифрация его единственного порта #FE, осуществляется только по адресному разряду A0, что казалось бы подтверждает правильность мифа о 32768 занятых адресах. И для некоторых, не совсем правильных клонов ZX Spectrum это утверждение будет вполне справедливым, но не для ZX Spectrum. Если взглянуть на принципиальную схему ZX Spectrum, то становится ясно, что в ULA для дешифрации его единственного порта приходит сигнал не IORQ/, а IORQGE. В чём же разница? Разница в том, что сигнал IORQGE будет активным только в том случае, если ни одно внешнее устройство не заявит, что выставленный процессором адрес порта принадлежит этому внешнему устройству. Т.е. любое внешнее устройство совершенно бесконфликтно может использовать любые адреса портов из диапазона, который согласно мифу занимает единственный порт ZX Spectrum. Т.е. в действительности, единственный порт ZX Spectrum занимает не 32768 чётных адреса, а только столько, сколько ему позволят внешние устройства, вплоть до того, что внешние устройства вправе вообще не оставить ULA ни одного адреса. Конечно, в этом случае внешним устройствам придётся взять на себя функции порта #FE реализованные в ULA.

Таким образом, как видите, благодаря остроумному техническому решению Альтвассера, с одной стороны удалось выполнить требования Синклера по минимизации количества используемых микросхем за счёт упрощения дешифрации, а с другой стороны отдать ULA ровно столько адресов портов, сколько необходимо, а именно - 1 адрес на запись и 8 адресов на чтение. Правда, при этом пришлось переложить на программное обеспечение функцию определения наличия того или иного порта внешних устройств в системе. И так бы и было, если бы в Sinclair Research хоть кто-то после ухода ведущих разработчиков понимал назначение сигнала IORQGE.. Но, увы, информация о назначении и важности этого сигнала покинула Sinclair Research вместе с её ведущими разработчиками. В результате, не только для Sinclair Research, но и для всех разработчиков как программного, так и аппаратного обеспечения назначение сигнала IORQGE так и осталось неизвестным. Именно поэтому, западные разработчики до сих пор так и не научились преодолевать ограничения накладываемые неполной дешифрацией портов УВВ, и бьются в истерике над несуществующей проблемой пересечения адресных диапазонов устройств. А разработчики ПО так и не поняли, что из 256 портов в диапазоне #xxFE необходимо использовать строго один порт на запись, а не занимать весь диапазон. К сожалению, всё существующее ПО уже не исправить, чтобы вернуть бездарно занятые адреса УВВ в диапазоне #xxFE. Одно лишь радует, что нашёлся единственный человек - Вячеслав Скутин aka Nemo, кто сумел понять ход мыслей Альтвассера, и воплотить их в отечественной системной шине NemoBus для периферийных устройств - клонов ZX Spectrum, которая является единственным стандартом, корректно воплотившим в себя идеи Ричарда Альтвассера.

Рассмотрим базовые принципы функционирования арбитра шины NemoBus, изобретённые Альтвассером и повторно переизобретённые Скутиным:

1) Первый базовый принцип функционирования арбитра шины NemoBus определяет способ формирования сигнала IORQGE периферийными устройствами. Суть изобретения состоит в том, что помимо сигнала M1/, в режиме арбитрирования захвата диапазона адресов портов УВВ для формирования сигнала IORQGE используются только адресные сигналы. Таким образом, в дешифраторе сигнала IORQGE, не используется сигнал IORQ/. Это связано с особенностью формирования этого сигнала процессором Z80, состоящей в том, что он вырабатывается спустя некоторое время после установления процессором валидного адреса. Таким образом, адресные сигналы, выставленные процессором раньше IORQ/, успевают пройти по цепям дешифраторов внешних устройств, подключенных к шине NemoBus, и все эти устройства успевают сформировать свои сигналы IORQGE ещё до момента активации сигнала IORQ/. Такое, превентивное формирование сигналов IORQGE, позволяет не тратить время на дешифрацию в периферийных устройствах после прихода IORQ/, и тем самым не укорачивать этот сигнал для других устройств включенных в последовательную цепочку, что важно, если периферийных устройств несколько.

2) Вторым базовым принципом является порядок включения периферийных устройств относительно устройств самого компьютера. Суть этого принципа состоит в том, что ULA компьютера всегда стоит в очереди последней, т.е. после всех периферийных устройств. Это значит, что сигнал IORQG/ в ULA компьютера приходит, только если все периферийные устройства это разрешат.

Исполнение обоих этих базовых принципов определяет соответствие устройства или шины идеям Альтвассера. Эти принципы соблюдены только в отечественных клонах с шиной NemoBus, а так же в оригинальных компьютерах ZX Spectrum. На Рис.1 приведена функциональная схема арбитра портов шины NemoBus для трёх слотов периферийных устройств.

В правильно заданном вопросе содержится половина ответа

А на картинке сигнал IORQ как раз используется. Кроме того, нужны же сигналы RD и WR. Как без них?

M1 - это вообще регенерация. Если смотреть на него и на шину адреса, то словим момент обращения к адресу памяти, а не порту ввода-вывода.

Но я ж не специалист ).

Интересно, сколько там длительность сигнала IORQ и сколько слотов может быть у компа, чтобы хватило длины сигнала? Пока там прощёлкает по всем слотам и сформируется итоговый сигнал IORQGE?

Скрытый текст

https://drive.google.com/drive/folde...xZ83juCuaBe32I

Scorpion ZS 256 Turbo+/GMX 2MB/SMUC v1.3 OP/CF-IDE 2GB/TS ARM/Covox #DD/FDD 5'25/FDD 3'5/AT Kbrd & Mouse Ctrl v2.5/Universal PS/2 Kbrd Ctrl/ZX WiFi

Leningrad 1/Sega Joy Adapter

DivGMX

ZX Spectrum +2A

ZX Evolution rev. C

TCK Computer 486DX2-66/512K Tridend 9000i/8MB SIMM72/CF-IDE 512MB/ESS 1869/CNet CN200/FDD 5'25/FDD 3'5

[свернуть]

Конечно. Идея в том, чтобы маскировать этот самый IORQ для других устройств, если текущий адрес твой. А он приходит раньше, поэтому по твоим адресам другие устройства даже иголки на IORQ не получат. Никто ничего тут не укорачивает. Сигналы RD и WR нужны уже для стробирования данных, они не участвуют в арбитраже и дешифрации.

izzx (16.03.2023)

Эту тему просматривают: 1 (пользователей: 0 , гостей: 1)